General Description

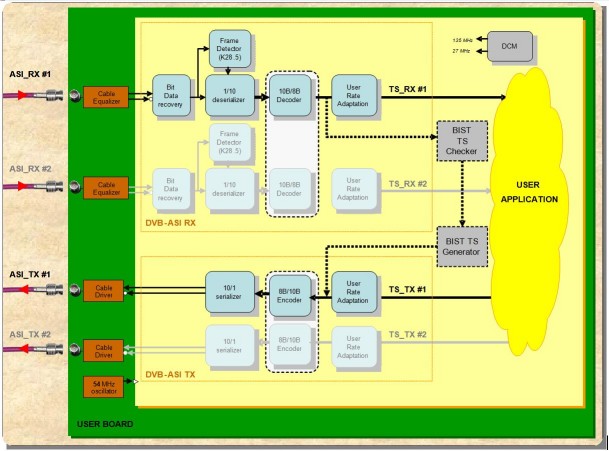

MW_ASI/SMPTE_SERDES cores implements related standards, by means of a precise and robust design, to inexpensive devices, (from Spartan3 up to 7Series families) using reduced FPGA resources.

This implies, at system level, two major benefits:

– No external deserializer devices are required

– Several instances of the core can be mapped in the same low-cost FPGA

MW_ASI/SMPTE_SERDES_RX performs three major tasks:

– Recovery and resampling serial data

– Framing data in the correct word boundary

– Decoding the 8B/10B encoded word

– TS flow delineation and synchronization

– TS flow adapting to user clock

MW_ASI/SMPTE_SERDES_TX adapts TS flow from yser clock to transmission clock, encodes words in 8B/10B format and serializes the data for transmission.

Clock infrastructures (PLLs, DCMs, BUFGs) are common to all core instances.

Features

- Compatible with DVB standard

- 310/270 Mbit Asynchronous

deserializer - Robust Jitter tolerance

- Polarity Insensitive

- 8B/10B coding

- TS framing

- Rate adaptation

- ASI received clock recovery (for “seamless” applications)

- Rx Clock Jitter compensation (up to 0.6 U.I.)

Performance and Resource Utilization

| Version | Family | Device | Slices | SliceReg | LUTs | DSP48E1 | BRAM | Speed(MHz) |

|---|---|---|---|---|---|---|---|---|

| RX dual | Spartan6 | XC6LX100 | 518 | 1100 | 1219 | 0 | 3 | 270 |

| RX dual | Artix®-7 | XC7A200T | 501 | 1100 | 1192 | 0 | 2 | 270 |

| RX dual | Zynq | Z-7020 | 501 | 1100 | 1192 | 0 | 2 | 270 |

| Version | Family | Device | Slices | SliceReg | LUTs | DSP48E1 | BRAM | Speed(MHz) |

|---|---|---|---|---|---|---|---|---|

| TX dual | Spartan6 | XC6LX100 | 167 | 482 | 347 | 0 | 3 | 270 |

| TX dual | Artix®-7 | XC7A200T | 158 | 482 | 338 | 0 | 2 | 270 |

| TX dual | Zynq | Z-7020 | 158 | 482 | 338 | 0 | 2 | 270 |

Support

The core, delivered as is, is warranted against defects for two years from the date of purchase. Sixty days of phone and email technical support are included, starting from the delivery date.

Verification

The core has been verified through extensive simulation and physical implementation with Vivado® Design Suite on Xilinx Spartan™ 6, Xilinx Artix™ 7 and Zynq-7000 technology.

Deliverables

The following deliverables are available:

- FPGA netlist and Xilinx ISE or Vivado® Design Suite constraint files

- User guide

- Block level design document

- VHDL test bench and test vectors

Optional deliverables:

- Fully synthesizable VHDL source code

- Synthesis script for XST

- tcl script for Vivado® Design Suite

Available Configuration

| Core P/N | Functionality |

|---|---|

| MW_ASI/SMPTE_SERDES_RX_single | single DVB Asi SerDes receiver |

| MW_ASI/SMPTE_SERDES_RX_dual | dual DVB Asi SerDes receiver |

| MW_ASI/SMPTE_SERDES_TX_single | single DVB Asi SerDes transmitter |

| MW_ASI/SMPTE_SERDES_TX_dual | dual DVB Asi SerDes transmitter |