General Description

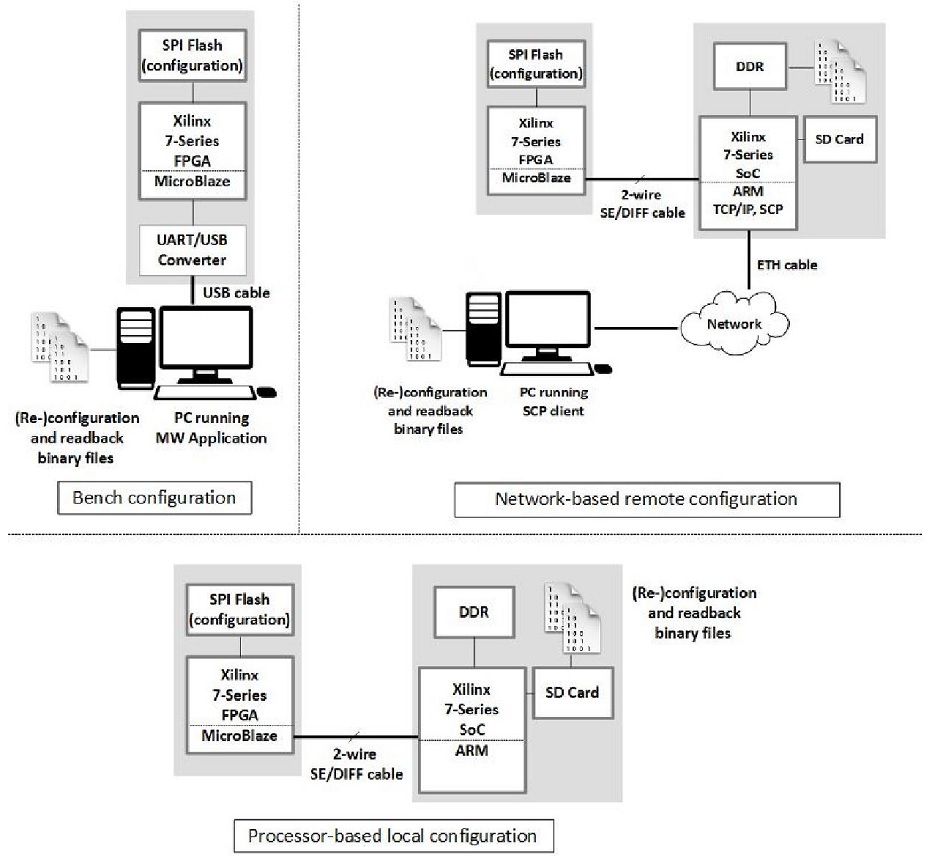

The MW_RR, FPGA Remote Reconfiguration, is a set of core, desktop and embedded software applications provided to enable the remote reconfiguration of an FPGA device, booting from an external Flash memory.

Remote configuration is a critical feature for complex electronic systems. In a wide range of applications, the hardware to be reconfigured is not directly accessible by the user, for debugging or upgrading purposes. Furthermore, the introduction of dedicated connections intended to remotely access the device is something difficult and expensive. Programmable System-on-Chip platforms greatly make Remote Configuration task easier. For instance an OS-based design gives the opportunity to load the new configuration file at many stages of software booting and execution and to use standard interfaces (Ethernet, USB, SD Card, etc.) to transfer such files.

When using traditional FPGAs, usually there are less degrees of freedom to achieve the task, and anyway the procedure is much more complex. The MW_RR exploits the benefits of standard OS solution to remotely reconfigure an FPGA. The advantage of such a kind of approach is threefold:

- When performing a batch (re-)configuration, there is no need to have a JTAG daisy-chain for all devices (thus enabling scalability). This is also true for configuration readback and verification.

- In a system with a processor/SoC driving the FPGA, the procedure is spread between the processor acting as a Master for both read and write operations and the FPGA being a slave.

- In any case, there is no need of using an additional off-chip JTAG programmer and a proprietary tool to interact with it.

Features

- 2-wire general purpose interface for device access.

- Functionality can be added even if it was not conceived at an early design stage.

- Readback capability.

- Desktop environment support.

- Embedded environment support.

- Network-based (SCP) configuration file transfer.

- Error protection over the duplex master-slave link.

- Multiple boot support.

- Zynq/Artix7 technology and ISE Xilinx/Vivado tool

Performance and Resource Utilization

| Family | Device | Slices | SliceReg | LUTs | DSP48E1 | BRAM | Speed(MHz) |

|---|---|---|---|---|---|---|---|

| Artix®-7 | XC7A200T | 6255 | 5600 | 6015 | 0 | 30 | - |

| Zynq | Z-7020 | 6255 | 5600 | 6015 | 0 | 30 | - |

Support

The core, delivered as is, is warranted against defects for two years from the date of purchase. Sixty days of phone and email technical support are included, starting from the delivery date.

Verification

The core has been verified through extensive simulation and physical implementation with Vivado® Design Suite on Xilinx Artix™ 7 and Zynq-7000 technology.

Deliverable

The following deliverables are available:

- FPGA netlist and Xilinx ISE or Vivado® Design Suite constraint files

- User guide

- Block level design document

- VHDL test bench and test vectors

Optional deliverables:

- Fully synthesizable VHDL source code

- Synthesis script for XST

- tcl script for Vivado® Design Suite