# **MW TS MUX Core**

# General Description

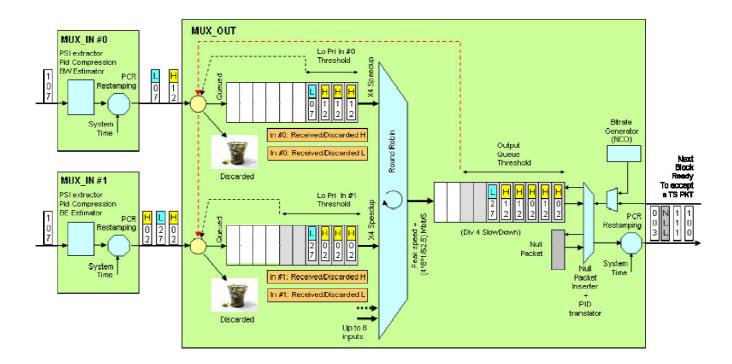

The MW\_TS\_MUX core is designed to multiplexer different transport stream and produce a single TS stream output.

It is composed by MW\_MUX\_IN core that operate in conjunction with the MW\_MUX\_OUT core. The first core handles a single MUX input port and performs the pre-processing operations necessary for the MW\_MUX\_OUT core to correctly generate an output TS stream.

The behaviour must be configured using an embedded MicroBlaze processor. Between the processor and the core an AXI interface is available, but also a PLB interface to be compliant with older design.

### MUX\_IN

The first block that processes the incoming Transport Stream is the PSI Extractor. It copies PSI information flows (e.g. PAT, PMT, etc.) to the MicroBlaze processor, in order to build the database of the contents available in the TS. PSI extraction permits to copy all packets belonging to a defined set of PIDs and to forward them to a packet FIFO connected to MicroBlaze processor. The defined set of PIDs is configurable via MicroBlaze processor. The packets received by the processor shall be read by the firmware according to the status of the packet FIFO to avoid FIFO overflows or overwrites.

According to an external programmable filtering/forwarding table the PID Compressor performs two main operations: it filters incoming programs, dropping unwanted PIDs and forwarding the remaining ones to the following elaboration stages using local ID (a reduced PID used for internal data handling); it forwards the selected PIDs either to a bandwidth estimator sub-module or to MUX\_OUT output stages, each with an individually programmable priority.

The bandwidth estimator monitors the data eventually provided by a preceding PID Compressor and performs bandwidth estimation on a per-second basis. Bandwidth statistics for the selected packets can be read by an external MicroBlaze processor accessing a dedicated register.

The PCR Adjust sub-module performs the first stage of a PCR re-stamping process subtracting the internal system time to the PCR value contained in incoming packets; a second PCR module will perform the second stage of this process prior to forwarding each packet outside the MUX OUT core.

Based on the information provided by the preceding PID Compressor, this TS Dispatcher sub-module will forward the filtered packets (now carrying a new local ID instead of the original PID) to the selected MUX OUT stages.

### MUX OUT

The core of the MW\_MUX\_OUT is the TS\_MUX submodule that can handle up to seven incoming data streams (each coming from a MUX\_IN stage) and a dedicated stream coming from an external MicroBlaze processor. An asymmetric 1-to-4 prioritized packet FIFO is provided for each input port in order to minimize packet losses. The module polls all incoming FIFOs and transfers available data to a single asymmetric 4-to-1 prioritized packet FIFO thus performing a merge of all incoming data streams. For each input port the module provides statistics related to the received and dropped high- and low-priority packets.

The PSI Inserter sub-module is used by an external MicroBlaze processor to inject informational packets into the resulting output stream using a dedicated input port of the TS\_MUX sub-module. This is necessary in order to merge the information previously gathered from all available PSI Extractor stages into the final TS after merging data coming from different independent input TS.

The Bandwidth Regulator sub-module enforces the TS output flow bit rate. A programmable output rate generator transmits 'packet credits' to the TS\_MUX output queue, according to the selected bit rate.

If a packet is available in the TS\_MUX output queue, it is read and sent to the BW\_REG output; otherwise a Null Packet is locally generated and sent to the output. If the transmission media connected to the output of the MW\_MUX\_OUT is bandwidth-limited (e.g. a DVB-x modulator configured to provide a certain throughput) the TS\_MUX bit rate has to be tuned to be minor or equal to the media capacity.

According to an external programmable translation table the PID Translator sub-module processes the incoming data stream substituting the local IDs contained in each packet with regular PIDs to be used for streaming the resulting data stream outside the MW MUX OUT core.

The PCR Adjust sub-module performs the final stage of the PCR re-stamping process adding the internal system time to the PCR contained in incoming packets prior to forwarding each packet outside the MUX core.

## **Features**

- DVB streams selection and routing

- It allows standard PSI parsing procedures to be implemented in the embedded processor

- 7 independent TS input ports and 1 PSI port to build custom output TS

- Priority level management

- Both AXI and PLB interface implemented

- 512 out of the 8192 possible incoming PIDs can be selected and internally reallocated

- Bandwidth estimation and PCR Adjusting to avoid video issues at the receiver side

- In conjunction with MW\_MUX\_OUT whatever routing topology can be achieved (e.g. multiple modulators feeding)

- Inexpensive implementation with reduced FPGA resources

| Slices | Slice Reg | LUTs | LUTRAM | BRAM/FIFO | DSP48E1 |

|--------|-----------|------|--------|-----------|---------|

| 3135   | 6008      | 6200 | 355    | 10        | 0       |

Validation in Xilinx Zynq device and Xilinx Vivado environment

#### **Architecture and Typical Application**

### **Support**

The core, delivered as is, is warranted against defects for two years from the date of purchase. Sixty days of phone and email technical support are included, starting from the delivery date.

#### Verification

The core has been verified through extensive simulation and physical implementation on Xilinx Spartan<sup>TM</sup> 6, Xilinx Artix<sup>TM</sup> 7 and Xilinx Zynq<sup>TM</sup> FPGA technology.

#### **Deliverables**

The following deliverables are available:

- FPGA netlist and Xilinx ISE constraint files

- User guide

- Block level design document

- VHDL test bench and test vectors

Optional deliverables:

- Fully synthesizable VHDL source code

- Synthesis script for XST

Please feel free to require any further information. Other MindWay Core Solutions are available, for standard or custom design applications, please visit our web site:

http://www.mindway-design.com

or send an e-mail at:

info@mindway-design.com